IT行業發展日新月異,電子產品快速輕薄短小化,印制電路板也面臨著高精度、高密度、細線化的挑戰。剛性線路板(PCB)的生產技術已經非常的成熟,但柔性線路板(FPC)仍處于起步階段,除了在PCB技術比較先進的美國、日本、韓國等國已經進行投產外,很多國家對該技術還比較陌生,我國的FPC技術還處于照抄照搬階段,自主研發的能力不強。FPC被廣泛的應用于IC封裝,計算機及其周邊設備,消費類電子產品、航空航天、軍事等各個領域。

隨著FPC的技術發展,特別是在3G通訊及計算機技術的持續推動下,電路訊號傳輸向高頻(射頻)類、高速(邏輯)類發展的需求量猛增,整個系統的信號傳輸完整、可靠、精確、無干擾、低噪音的保證性要求提高,這就要求電路性能必須能夠使信號在傳輸過程中不發生反射現象、信號保持完整、降低傳輸損耗、阻抗良好匹配。且當訊號線長度越長,訊號線傳輸的信號頻率越高,驅動端、訊號線與接收端的阻抗匹配需求和信號完整性(SI)要求就越強烈,而特性阻抗是解決信號完整性問題的核心所在。

特性阻抗的直接影響因素有:板材的介電常數(Er)、訊號線線寬(W)、訊號線間距(S)、訊號線線厚(T)、介質厚度(H)、阻焊層厚度(H1)等,各種影響因素的貢獻度并不是一成不變的,過程控制建議針對不同的特性阻抗板抓住重點控制因子。所以,通過控制電路板的制造工藝來控制線路的W、T、H及使用不同的PCB基材,就能有效控制電路板的特性阻抗,為信號的完整性提供有利的保障。

高精度特性阻抗板的工程設計

特性阻抗理論設計主要有三種途徑:通過理論公式計算、通過模擬仿真評估、通過專業軟件分析;第一種方式控制精度不高;第二種方法速度慢,但在特殊情形下很有效;第三種方法運作速度快且分析精度高。

但眾所周知,其實在任何多層PCB疊層結構中,訊號線周圍的電介質在一定程度上來講均是各向異性的,通常玻纖的相對介電常數(Er)在6.0左右、樹脂的Er在3.1左右,各類core及PP的Er在4.2左右,要求特征阻抗值為50W±10%,本次設計選用行業中制造阻抗板12/25/12軟板制作,再通過Polar-Si9000來模擬得出所需要的線寬,線寬設計為52mm。特征阻抗當頻率超過1GB時隨著頻率的增加而衰減明顯。

基板精細線路制作關鍵工藝研究

圖形轉移工藝是將所需要的電路圖形制成掩膜(或照相底版),然后通過曝光將掩膜上的電路圖形轉移到涂覆有感光抗蝕層的覆銅板上,最后通過顯影工藝制成所需要的電路圖形。圖形轉移工藝的具體工藝流程如下:

光致抗蝕劑的選擇→涂覆抗蝕層→曝光→顯影

目前,測試印制電路板特性阻抗最常用的儀器是TDR(時域反射計)。TDR使用階躍信號發生儀和示波器,在被測的傳輸線上發送一個快速的上升沿,在特定的點上用示波器觀察反射電壓波形。TDR允許測量阻抗隨線路的長度而改變,用一個上升時間很快的脈沖來模擬高速邏輯功能方面的測試。利用阻抗不連續產生的反射的電壓來表示出阻抗的變化,并利用反射電壓來計算出整個線路上面的特性阻抗。當傳輸線上存在寄生電容、電感(如過孔、線寬變化、近距離鋪銅等)時,在TDR曲線上可以反映出寄生參數引起的阻抗不連續(阻抗值降低、升高),為提高特性阻抗測試精度,必須減少TDR測試誤差源。而TDR儀器的階越脈沖上升時間是影響其分辨率的最關鍵因素。TDR的上升沿時間越短,其分辨率就越高。

特性阻抗的直接影響因素有:板材的介電常數(Er)、訊號線線寬(W)、訊號線間距(S)、訊號線線厚(T)、介質厚度(H)、阻焊層厚度(H1)等,各種影響因素的貢獻度并不是一成不變的,過程控制建議針對不同的特性阻抗板抓住重點控制因子。在其它條件不變時,精確控制電路板的制造工藝來控制線路的W,就能有效控制電路板的特性阻抗,同時屏蔽膜的覆蓋為信號的完整性提供有利的保障。

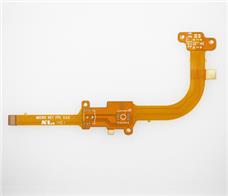

醫療設備控制器軟板

醫療設備控制器軟板 數碼相機軟板

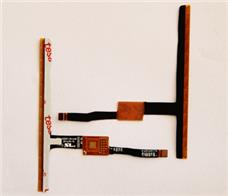

數碼相機軟板 手機電容屏軟板

手機電容屏軟板